|

modm API documentation

|

|

modm API documentation

|

#include <modm/platform/spi/spi_hal_5.hpp>

Public Types | |

| enum | CrcInit : uint32_t { AllZeros = 0, AllOnes = SPI_CR1_TCRCINI | SPI_CR1_RCRCINI, Mask = AllOnes } |

| enum | DataMode : uint32_t { DataMode::Mode0 = 0b00, DataMode::Mode1 = SPI_CFG2_CPHA, DataMode::Mode2 = SPI_CFG2_CPOL, Mode3 = SPI_CFG2_CPOL | SPI_CFG2_CPHA, Mask = Mode3 } |

| enum | DataOrder : uint32_t { MsbFirst = 0b0, LsbFirst = SPI_CFG2_LSBFRST, Mask = LsbFirst } |

| enum | DataSize : uint32_t { Bit4 = 3, Bit5 = 4, Bit6 = 5, Bit7 = 6, Bit8 = 7, Bit9 = 8, Bit10 = 9, Bit11 = 10, Bit12 = 11, Bit13 = 12, Bit14 = 13, Bit15 = 14, Bit16 = 15, Bit17 = 16, Bit18 = 17, Bit19 = 18, Bit20 = 19, Bit21 = 20, Bit22 = 21, Bit23 = 22, Bit24 = 23, Bit25 = 24, Bit26 = 25, Bit27 = 26, Bit28 = 27, Bit29 = 28, Bit30 = 29, Bit31 = 30, Bit32 = 31 } |

| enum | DmaMode : uint32_t { None = 0, Tx = SPI_CFG1_TXDMAEN, Rx = SPI_CFG1_RXDMAEN, Mask = SPI_CFG1_TXDMAEN | SPI_CFG1_RXDMAEN } |

| enum | DuplexMode : uint32_t { FullDuplex = 0, TransmitOnly = SPI_CFG2_COMM_0, ReceiveOnly = SPI_CFG2_COMM_1, HalfDuplex = SPI_CFG2_COMM_1 | SPI_CFG2_COMM_0, Mask = HalfDuplex } |

| enum | Interrupt : uint32_t { RxPacketAvailable = SPI_IER_RXPIE, TxPacketSpaceAvailable = SPI_IER_TXPIE, DuplexPacket = SPI_IER_DXPIE, EndOfTransfer = SPI_IER_EOTIE, TxTransferFilled = SPI_IER_TXTFIE, Underrun = SPI_IER_UDRIE, Overrun = SPI_IER_OVRIE, CrcError = SPI_IER_CRCEIE, TiFrameError = SPI_IER_TIFREIE, ModeFault = SPI_IER_MODFIE, Reload = SPI_IER_TSERFIE } |

| enum | MasterSelection : uint32_t { Slave = 0, Master = SPI_CFG2_MASTER, Mask = Master } |

| enum | Prescaler : uint32_t { Div2 = 0, Div4 = SPI_CFG1_MBR_0, Div8 = SPI_CFG1_MBR_1, Div16 = SPI_CFG1_MBR_1 | SPI_CFG1_MBR_0, Div32 = SPI_CFG1_MBR_2, Div64 = SPI_CFG1_MBR_2 | SPI_CFG1_MBR_0, Div128 = SPI_CFG1_MBR_2 | SPI_CFG1_MBR_1, Div256 = SPI_CFG1_MBR_2 | SPI_CFG1_MBR_1 | SPI_CFG1_MBR_0 } |

| enum | SlaveSelectMode { HardwareGpio, Software = SPI_CFG2_SSM } |

| enum | SlaveSelectPolarity { ActiveLow = 0, ActiveHigh = SPI_CFG2_SSIOP } |

| enum | StatusFlag : uint32_t { RxPacketAvailable = SPI_SR_RXP, TxPacketSpaceAvailable = SPI_SR_TXP, DuplexPacket = SPI_SR_DXP, EndOfTransfer = SPI_SR_EOT, TxTransferFilled = SPI_SR_TXTF, Underrun = SPI_SR_UDR, Overrun = SPI_SR_OVR, CrcError = SPI_SR_CRCE, TiFrameError = SPI_SR_TIFRE, ModeFault = SPI_SR_MODF, Reload = SPI_SR_TSERF, Suspension = SPI_SR_SUSP, TxTransferComplete = SPI_SR_TXC, RxFifoLevel1 = SPI_SR_RXPLVL_1, RxFifoLevel0 = SPI_SR_RXPLVL_0, RxFifoWordNotEmpty = SPI_SR_RXWNE } |

Public Member Functions | |

| MODM_FLAGS32 (Interrupt) | |

| MODM_FLAGS32 (StatusFlag) | |

| MODM_FLAGS32 (DmaMode) | |

Static Public Member Functions | |

| static void | enableClock () |

| static void | disableClock () |

| static void | initialize (Prescaler prescaler, MasterSelection masterSelection=MasterSelection::Master, DataMode dataMode=DataMode::Mode0, DataOrder dataOrder=DataOrder::MsbFirst, DataSize dataSize=DataSize::Bit8) |

| static void | enableTransfer () |

| static void | disableTransfer () |

| static bool | isTransferEnabled () |

| static void | startMasterTransfer () |

| static void | suspendMasterTransfer () |

| static void | setDataMode (DataMode dataMode) |

| static void | setDataOrder (DataOrder dataOrder) |

| static void | setDataSize (DataSize dataSize) |

| static void | setMasterSelection (MasterSelection masterSelection) |

| static void | setDuplexMode (DuplexMode mode) |

| static void | setCrcEnabled (bool enabled) |

| static void | setCrcSize (DataSize crcSize) |

| static void | setCrcPolynomial (uint32_t poly) |

| static void | setCrcInitialValue (CrcInit init) |

| static void | setDmaMode (DmaMode_t mode) |

| static void | setTransferSize (uint16_t size, uint16_t reload=0) |

| static void | setSlaveSelectMode (SlaveSelectMode mode) |

| static void | setSlaveSelectPolarity (SlaveSelectPolarity polarity) |

| static void | setSlaveSelectState (bool state) |

| static uint32_t | transmitCrc () |

| static uint32_t | receiveCrc () |

| static volatile uint32_t * | transmitRegister () |

| static const volatile uint32_t * | receiveRegister () |

| static StatusFlag_t | status () |

| static bool | isTransferCompleted () |

| static bool | isTxCompleted () |

| static bool | isTxFifoFull () |

| static bool | isRxDataAvailable () |

| static void | write (uint8_t data) |

| static void | write16 (uint16_t data) |

| static void | write32 (uint32_t data) |

| static uint8_t | read () |

| static uint16_t | read16 () |

| static uint32_t | read32 () |

| static void | enableInterruptVector (bool enable, uint32_t priority) |

| static void | enableInterrupt (Interrupt_t interrupt) |

| static void | disableInterrupt (Interrupt_t interrupt) |

| static void | acknowledgeInterruptFlags (StatusFlag_t flags) |

Static Public Attributes | |

| static constexpr auto | peripheral = Peripheral::Spi5 |

| static constexpr DataSize | MaxDataBits = DataSize::Bit16 |

| static constexpr DataSize | MaxCrcBits = DataSize::Bit16 |

| static constexpr std::size_t | MaxTransferSize = 65535 |

| Maximum permitted size for fixed size transfers. | |

| static constexpr std::size_t | FifoSize = 8 |

| Size of FIFO in bytes. | |

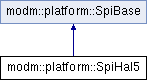

Serial peripheral interface (SPI5)

|

inheritedstrong |

|

static |

|

static |

|

static |

|

static |

|

static |

Read an 8-bit value from the receive data register.

|

static |

Read a 16-bit value from the receive data register.

|

static |

Read a 32-bit value from the receive data register.

|

static |

Configure total amount of data items of transfer Set size to 0 for unlimited transfers.

| reload | Next transfer size after reload |

|

static |

Write up to 8 Bit to the transmit data register

|

static |

Write up to 16 Bit to the data register

|

static |

Write up to 32 Bit to the transmit data register